详情介绍

Cadence发布了其仿真产品Sigrity系列的新版本—Sigrity 2017 ,带来了多项新的仿真功能,专为加速PCB电源完整性及信号完整性仿真流程量身打造。内置总PCIe 4.0工具包,确保信号完整性符合今年即将发布的全新 PCIe标准。新加入的Allegro PowerTree拓扑检视器及编辑器能帮助客户快速评估设计流程初期的功率输出方案。

全新发布的Sigrity 2017采用分析模型库管理器,实现对电源完整性模型内容库的管理,所有模型皆可实现自动存储并在复用设计组件时从分析模型管理器内容库中取回。这一流程此前仅支持手动重复操作,现在则可以实现全自动化,大幅加速设计及产品开发。

Sigrity 2017还将最新PCIe技术与高速互联结合,助设计师实时确保信号完整性。内置的Sigrity System SI 串联分析工具包括PCIe 4.0接口标准工具包,无需人工对照标准文件以检查并评估,即可自动验证信号质量标准。

软件介绍:

高科技企业开发复杂的芯片,封装和单板努力克服由于飞速增长的IC速度和数据传输速率联合引起的供电电压的降低,更高密度,越来越小型化的结构引起的电源完整性和信号完整性问题。同时,更高的I/O数目,多堆叠的芯片和封装以及更高的电气性能约束都使得IC封装物理设计更加复杂。

Cadence具有突破型进展的解决方案,基于Sigrity专利技术,解决这些设计挑战。该解决方案致力于完整的电源供电系统分析跨越了芯片,封装和单板;系统级的信号完整性(SI)分析,包含高速信号传输同步反转噪声和单个和多个芯片封装,最先进的 3D封装以及系统级封装(SiPs)的高级物理设计。

Sigrity 2017安装教程:

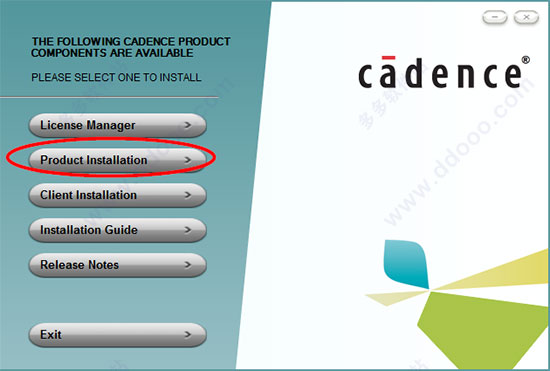

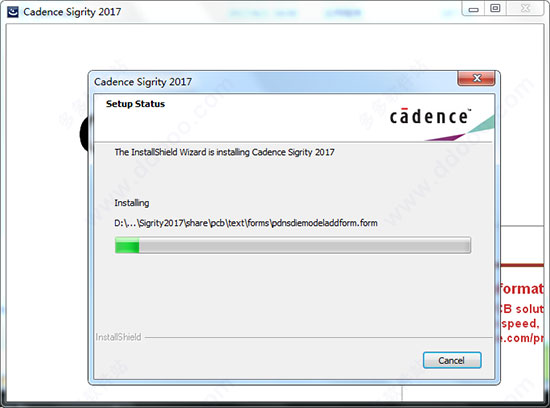

1、解压安装包首先打开“SIG17.00”目录,运行“setup.exe”,选择“Product installation”

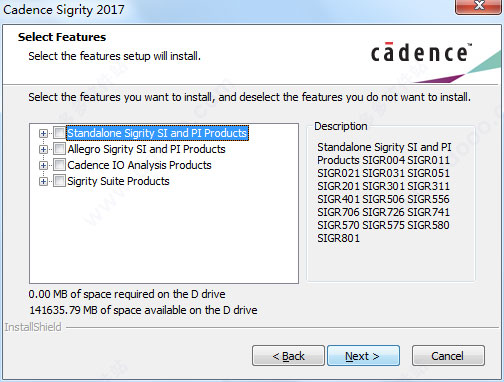

2、根据提示选择安装目录和功能即可

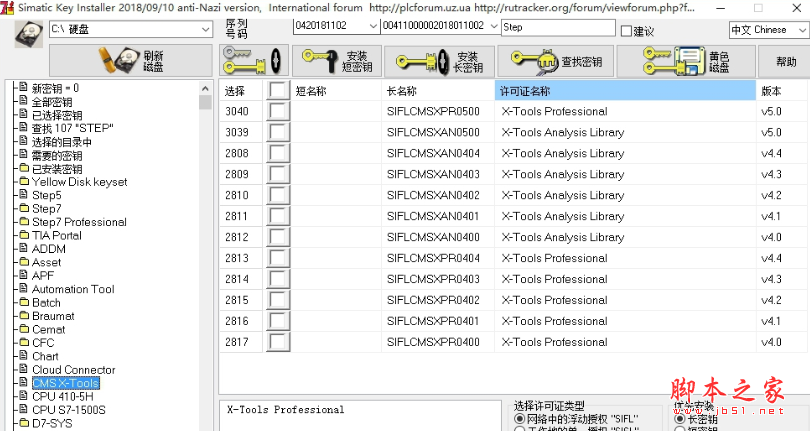

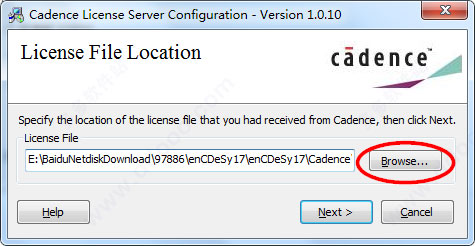

3、然后点击“License Manager”开始安装许可

4、弹出许可界面,选择点击Browse

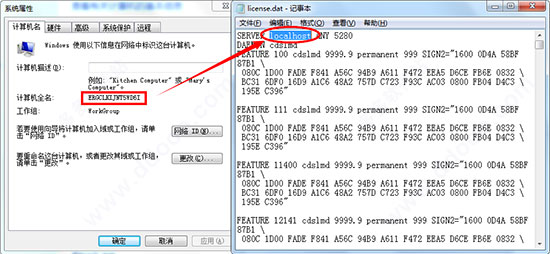

5、以记事本方式打开安装包“Patch”目录下的“license.dat”,将localhost修改为计算机名,保存退出,然后载入(计算机名可以右键点击计算机选择属性查看)

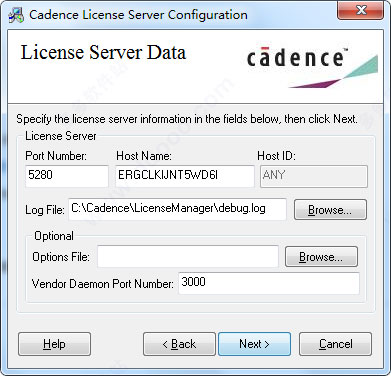

6、确认信息和许可中一致

7、许可安装完成后,将“run.bat”和“patch.exe”复制安装目录下运行即可,默认目录为C:\Cadence\Sigrity2017

Sigrity 2017新特性:

Cadence 发布 Sigrity 2017 版本,除了效能提升之外,各相关程序新增功能如下:

·PowerDC – PowerTree 电源回路的拓扑结构

·Speed2000 – 新增 ESD 仿真的流程

·PowerSI – Special void 设定自动化

·3DEM – Partial Inductance 及 SPICE 模型的提取

·SystemSI – 新增 PCI-E Gen4 和 P8+ OpenPOWER Compliance Kit

·XtractIM – XtractIM EPA 的 HTML 报告可与 APD 作交互查询

·T2B – 支持 IBIS 6.1 和 Random Pattern

新功能介绍:

1、PowerTreePower Tree 是一种由电路图或 PCB layout 抽出可视觉化的电源回路的拓扑结构资料的工具。除了产生 Power Tree 外,里面所有的元件属性都可透过手动添加或利用 AMM Model 来带出。它可以协助使用者很容易地进行早期电路功耗的评估及后续的自动化环境及条件的设置。 PowerTree可以单独执行,或是与整合到 PowerDC、OptimizePI 和 Allegro Sigrity PI。

PowerTree 为 DC 分析目的提供以下功能:

·产生一个直观的由 VRM 到 Sink 端的电源拓扑结构

·由电路图 /PCB 布局中提取元件属性

·易于修改的元件资料

·自动识别所有电源网络以进行分析

·轻松查找/追踪电路图中的 ECO 变更

·执行 pre-Layout 的直流分析

·与 AMM model Library 沟通以便使用模型数据

·可储存/载入重复使用 PowerTree 档案

2、Speed2000

新增 ESD Simulation 的工作流程

在 Sigrity2017 中,Speed2000 新增静电分析功能,用来检查放电问题对设计的影响。 ESD 可以定义为两个带电物体之间的静电流,有可能因为接触、短路或因介电质的损坏而触发。

例如:

·通过与敏感设备的人类接触,人体触摸对引发放电现象往往会超过 4,000V。

·USB 缆线因具备供电能力,因此在端口接触瞬间亦会引发放电现象。

·因来自触摸电子设备或系统的人体的静电放电可以产生数千伏特电压和几安培电流,这个现象可以容易导致 IC 内部电路损坏。以下是可能由 ESD 引起的损坏状况:

·设备或系统完全故障

·未预测的设备或系统行为

·电磁辐射的干扰

3、增强对 Allegro 图档的支持

·支持 PCB 背钻结构。

·支持当 brd 文件时转换成 .spd 格式时对背钻孔结构的解析和仿真。

·支持 Tabs routing 布线设计转换成 .spd 格式和仿真。

4、Special void 设定自动化

Void 的大小唯有极小于欲仿真的信号波长方可忽略以便加快仿真速度,因此需要有经验的工程师进行设定避免仿真偏差。新增的自动化功能可以根据仿真的频率自动设定 special void,简化设定难度并加快仿真速度。

5、改善低频的准确性

·以往在提取参数时,如果线路中有串并联被动元件,PowerSI 会一起考虑进来。但是 PCB 分布的众多解耦合电容会使电源平面在低频会有很多共振点,曲线变化很大导致分别由低频仿真器与高频仿真器个别运算的结果结合的曲线 fitting 比较困难。因此比较好的作法是先提取未挂载被动元件的线路参数,之后再与被动元件的参数结合在一起。

·支持 Allegro 档案中的背钻结构

·PowerSI 可以直接支持 Allegro 档案设定的背钻结构,无须在PowerSI里面额外设定。

6、3DEM

·支持多接脚被动元件的 SPICE model

·Partial Inductance 及 SPICE 模型的提取

·支持 quasi-static solver提取的 Partial Inductance,包含电源、信号甚至接地的走线并输出成 RLC SPICE 模型或矩阵形式的电感值的文档。

7、PowerDC

Thermal Flow Enhancements

8、热分析流程增强:

·强化存档/载入分析结果的功能,以支持 2D / 3D 应力分布

·添加热传递系数值到签核报告中

·改进散热器编辑过程,避免在编辑模型后发生重复点击确定按钮

·强化电源和温度分布图形档案

下载地址

人气软件

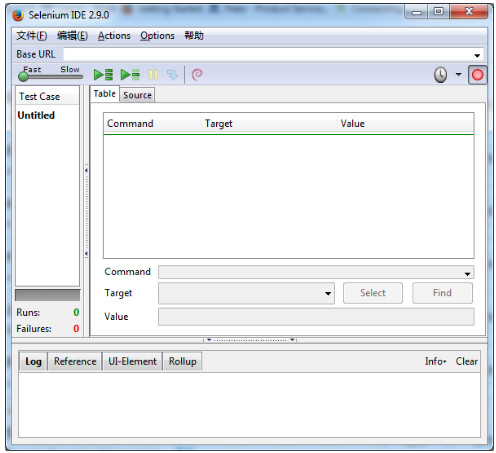

selenium IDE安装包 V2.9.0 (附安装教程)

minitab2021 v21.4.2 中文破解版(附使用教程) 64位

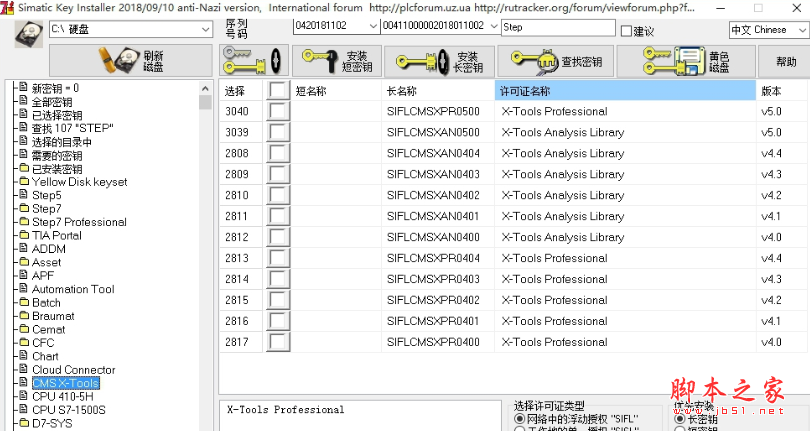

西门子全系列软件授权工具Sim EKB Install v2023.11.24 最新绿色

ANSYS Products 2024 R2.03 (SP3) x64 中文免费授权版(附安装教

Sidefx Houdini FX(电影特效魔术师) v12.5 2013 english 附详细

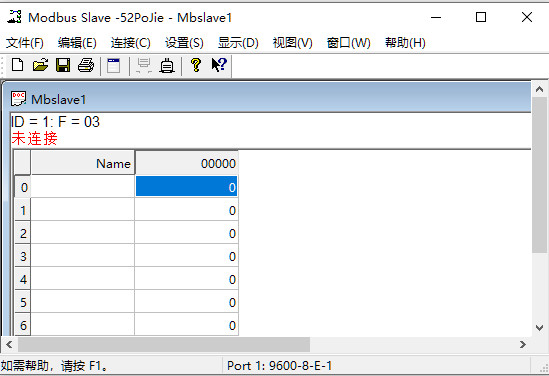

Modbus slave调试工具 v7.4.4 绿色免安装汉化版 64位

KISSsoft 2022 SP3-SP5 x64 中文免费破解版(附许可文件+教程)

西门子PCL编程软件STEP7 MicroWIN SMART V2.8 官方最新版

EPLAN Electric P8 2024.0.3 (21408) x64 中文完美激活版(附安装

EPLAN Electric P8 2022 中文授权破解版(含补丁+安装教程)

相关文章

-

Siemens SIMATIC PCS 7 V10 2023.7 中文完整授权版(附教程)

Siemens SIMATIC PCS 7 V10 2023.7 中文完整授权版(附教程)SIMATIC PCS 7是一款性能可靠的分布式控制系统,先进的过程控制系统非常适合工厂应用,作为强大的系统,它具有灵活的适应性,该系统可确保工厂全生命周期中的平稳流程、优...

-

CNC编程软件 GibbsCAM 2025 v25.0.41.0 x64 中文授权免费版(附安装教程)

CNC编程软件 GibbsCAM 2025 v25.0.41.0 x64 中文授权免费版(附安装教程)GibbsCAM是一款易于学习且直观的CAM软件,非常适合企业中的各类用户。无论您是经验丰富的技术专家还是刚入门的新手,GibbsCAM的高效编程能力都能帮助您实现最高75%的编程效...

-

Cadence SPB OrCAD X/Allegro X Design Platform 2024 v24.10.000 完整免费版

Cadence SPB OrCAD X/Allegro X Design Platform 2024 v24.10.000 完整免费版Cadence设计系统公司发布了Cadence OrCAD X Design Platform 2024 (OrCAD X and Allegro X),此次更新的重点是可用性、集成分析和自动化,包括BOM预测和预测分析、数据管理...

-

齿轮设计软件 KISSsoft 2024 SP2 x64 中文免费版(附安装教程)

齿轮设计软件 KISSsoft 2024 SP2 x64 中文免费版(附安装教程)KISSsoft 2024是一款专业的齿轮传动设计分析软件,它是用于设计、优化和分析机器元件的模块化计算系统,广泛应用于工业领域、航空航天领域、车辆行业等,本次提供的是KISSs...

-

Keysight PathWave Advanced Design System (ADS) 2025 完整版(附安装教程)

Keysight PathWave Advanced Design System (ADS) 2025 完整版(附安装教程)Advanced Design System (ADS) 2025又称高级软件设计系统,是由Keysight是德科技公司开发的电子设计自动化软件,适用于射频、微波和信号完整性应用,本次提供的是ADS2025最...

-

EPLAN Electric P8 2025 v2025.0.0.0 官方正式安装版

EPLAN Electric P8 2025 v2025.0.0.0 官方正式安装版EPLAN Electric P8 2025正式版目前已经发布了,是一款功能强大的电气工程设计软件,新版本对PLC、电缆、端子进行了更新,创新的功能和改善将使您的设计更加高效...

下载声明

☉ 解压密码:www.jb51.net 就是本站主域名,希望大家看清楚,[ 分享码的获取方法 ]可以参考这篇文章

☉ 推荐使用 [ 迅雷 ] 下载,使用 [ WinRAR v5 ] 以上版本解压本站软件。

☉ 如果这个软件总是不能下载的请在评论中留言,我们会尽快修复,谢谢!

☉ 下载本站资源,如果服务器暂不能下载请过一段时间重试!或者多试试几个下载地址

☉ 如果遇到什么问题,请评论留言,我们定会解决问题,谢谢大家支持!

☉ 本站提供的一些商业软件是供学习研究之用,如用于商业用途,请购买正版。

☉ 本站提供的Cadence Sigrity(仿真软件) 2017 特别版(附安装教程+破解文件)资源来源互联网,版权归该下载资源的合法拥有者所有。