详情介绍

HDL Designer Series(HDS) 2021破解版是一个强大的基于 HDL 的环境,全球各个工程师和工程团队使用它来分析、创建和管理复杂的 FPGA 和 ASIC 设计。HDL Designer Series(HDS) 不仅是功能强大的交互式 HDL 可视化和创建工具,提供从头开始进行设计创建所需要的一切,轻松创建、分析以及管理您的设计,将复杂的设计简化并提高工作效率!您将拥有一整套完整的高级设计工具和编辑器,从而能够获得更好的方法以及更快的速度来进行大型设计的创建!与传统的方法不同,您可以更快的进行代码的分析、评估和重用,提供代码的完整性分析、连接完整性分析、HDL 代码质量评估和设计可视化,在整个设计过程中,您都可以很好的掌控其细节和过程,提高生产力的同时实现可重复和可预测的设计过程。

Mentor Graphics HDL Designer 系列优势概述

HDL Designer 协助工程师分析、评估和可视化复杂的 RTL 设计,提供代码完整性分析、连接完整性分析、HDL 代码质量评估和设计可视化。

与代码分析密切相关的是代码创建。 HDL Designer 为工程师提供了一套高级设计编辑器以促进开发:基于接口的设计电子表格编辑器 (IBD) 和框图、状态机、真值表、流程图和算法状态机编辑器。 HDL Designer 包括一个与 EMACS/vi 兼容、支持 HDL 的文本编辑器,以补充这些编辑器。

与设计分析和创作相结合,设计管理是设计师的第三项重要工作。除了管理设计数据,团队还必须在整个设计流程中管理项目。

HDL Designer 通过为设计人员提供与流程、数据和版本管理解决方案中的其他设计工具的接口来解决设计管理问题。 HDL Designer 可通过 HTML、OLE、打印和图形导出实现简单的设计和完整的项目文档。

Mentor Graphics HDL Designer 系列功能概述

以 VHDL、Verilog 和 SystemVerilog 管理复杂的 ASIC 或 FPGA 设计

加速 RTL 重用

广泛的设计检查规则和规则集

交互式 HDL 可视化和创建工具

自动文档功能和报告

智能调试分析

并行设计输入和检查

快速评估重用代码质量并增加设计理解

使用文本、表格和图形高效地创建 RTL 设计

交互式管理设计流程和所有项目数据

快速生成文档

加速 IP 存储库填充

管理和理解代码关系

提高语言能力和结果

总结和量化代码特征

自动化和简化数据管理

设计、测量和记录实际代码重用

技术细节和系统要求

支持的操作系统:Windows 11 / Windows 10 / Windows 8.1 / Windows 7

处理器:多核 Intel 系列或更高版本,Xeon 或 AMD 同等产品

内存:4GB(推荐 8GB 或更多)

可用硬盘空间:推荐 4GB 或更多

功能特色

1、管理操作由设计管理器提供,包括一个项目管理器、多个设计浏览器、版本管理界面以及模板和任务管理器。

2、项目管理器允许您管理指定设计数据位置的库映射。可以创建或修改项目并将其存储为个人用户或共享团队资源。

3、您可以打开多个设计浏览器以将您的设计数据显示为设计单元、HDL文件或逻辑设计对象。可以在单独的层次结构浏览器中探索任何设计对象下的完整设计层次结构。额外的浏览器可用于探索与源(侧数据)和下游工具所需或产生的数据相关的额外信息,例如模拟或综合(下游数据)。提供了一系列通用版本管理工具的接口,包括:Subversion®、IBM Rational ClearCase®和CVS。CVS包含在发行版中,当其他系统在您的文件系统上可用时,可以选择它们。

4、任务管理器支持下游工具和设计流程的可定制接口。

5、提供默认任务以支持从图形源视图以及使用一系列行业标准工具进行编译、仿真和综合的HDL生成。使用Tcl定义任务以运行外部程序或Tcl脚本。可以将单个任务添加到流中以创建完整的操作序列。支持以下模拟器:ModelSim®、Questa®、Cadence®Incisive®和Synopsys®VCS®/VCSi。还为以下综合工具提供了默认任务:Precision®Synthesis、LeonardoSpectrum™、Synopsys®Design Compiler®和Synplify®/Synplify-Pro。为以下FPGA供应商工具提供了直接集成:Xilinx®ISE®、Altera®Quartus®和Microsemi®Libero®。仿真分析器接口提供错误交叉引用和动画工具以协助设计调试操作。为ModelSim和QuestaSim提供完整的调试支持。

6、模板管理器为HDL文本视图提供默认模板,可以对其进行编辑以支持您的本地设计标准,包括每个视图类型的多个替代模板。

7、设计经理支持由每个单独用户维护的任务和模板,以及由团队管理员维护的共享团队资源。

8、设计管理器包括一个集成的DesignPad设计感知、语言敏感文本编辑器,用于创建和维护HDL文本设计文件。或者,可以使用一系列外部文本编辑器来编辑和/或查看文本文件。

9、也可以使用图形和表格编辑器进行设计输入。可以使用表格IO或图形符号编辑器来描述组件接口。可以使用图形框图编辑器或使用基于接口的设计(IBD)视图以表格/电子表格格式维护分层设计中设计单元之间的互连。叶级视图可以使用HDL文本视图指定,也可以使用状态图、算法状态机、流程图和真值表编辑器以图形方式指定。

10、HDL2Graphics™功能可以导入任何完整或部分基于文本的HDL设计,并将文本描述转换为完全可编辑的图形或表格视图的层次结构。

11、与设计输入类似,转换后的设计结构可以表示为图形框图或表格IBD视图。叶级视图可以表示为状态图、流程图或HDL文本视图。生成的描述可以打印或导出为HTML网页以用于设计文档。在Windows上,可以使用对象链接和嵌入(OLE)功能将任何文本或图形视图直接包含在文档工具中。

12、现有的HDL设计可以导入到HDL Designer系列数据模型中,同时保持文件结构和设计数据的完整性。导入的代码可以可视化为图形框图、表格IBD视图、状态图或流程图,以帮助理解和记录。可以对任何可视化进行非逻辑更改。

13、版本管理可用于您导入的HDL文本和渲染的图形视图,并且设计浏览器可用于遍历设计单元之间的关系。

14、ModuleWare库提供了一系列标准组件,可以在图形或HDL文本设计中实例化(使用DesignPad编辑器时)。HDL Designer包括DesignChecker,这是一个功能齐全的静态设计检查和分析工具,使每个工程师都能找到并纠正在仿真和综合之前的设计过程早期的编码违规。可配置的基本规则允许项目经理创建所需的检查,这些检查补充了所提供的规则集,包括RTL综合规则、SystemVerilog和OVM/UVM验证规则、复杂的设计范围规则以及可读性和一致性的样式规则。策略和规则集可以在多个团队之间共享,具有全面的排除机制,允许在需要时放弃规则。整个设计过程中的自动化设计检查以及交互式违规分析和报告生成可帮助设计团队遵守安全标准和合规性要求。

15、HDL Designer通过其寄存器助手技术提供寄存器管理功能。注册助手允许您在一个中心位置更改注册规范并自动生成/更新许多派生输出。寄存器和存储器描述可以从多种来源(包括IP-XACT、XML和电子表格(CSV)格式)导入到一个内聚的、可扩展的数据模型中,该模型描述了块、子块、映射、寄存器、字段和存储器的层次结构。可定制的DRC检查确保数据的一致性,完整的API允许添加定制的输入转换器和输出生成器。输出包括用于验证的OVM和UVM寄存器包、可合成的VHDL和Verilog RTL代码、用于驱动程序开发的C头文件以及用于通信和记录保存的HTML超链接文档。

16、包含的SystemVerilog-VHDL助手工具提供了可定制的模板代码生成器,极大地促进了复杂UVM/OVM测试平台基础设施的正确构建创建。文本编辑提供拖放实例化、自动完成和自动连接功能以及强大的导航功能。代码结构可以表示为互连的UVM/OVM组件,类关系可以可视化为类图。无论在浏览器、文本或图表中如何表示,该工具都能理解给定的对象。几个内置浏览器提供了设计的不同观点,并能够在它们之间进行交叉引用。构建管理器自动创建和执行Makefile,以增量方式执行编译、分析和模拟步骤。除了Verilog RTL设计编辑支持之外,SystemVerilog-VHDL Assistant还提供了用于创建基于文本的VHDL RTL设计的高级编辑功能。

新增功能

1、HDL Designer

- Subversion 回滚支持

- Xilinx Vivado 2020.2 支持

- Intel Quartus Prime 20.1 标准版支持

2、SystemVerilog -VHDL Assistant

- 一般性能和稳定性改进

- Xilinx Vivado 2020.2 支持

3、Register Assistant

- IP-XACT 寄存器定义中的多地址块支持

4、外部工具支持

HDL Designer Series 工具接口已经过某些外部工具版本的测试。某些工具可能并非在所有平台上都可用。

5、停止

使用的工具不再支持以下版本管理界面:

- ClioSoft SOS

- GNU 修订控制系统 (RCS)

- Microsoft 或 Mainsoft Visual SourceSafe (VSS)

6、Java 运行时环境

SystemVerilog-VHDL 助手和注册助手在 OpenJDK JRE 8u252 上运行。

下载地址

人气软件

selenium IDE安装包 V2.9.0 (附安装教程)

minitab2021 v21.4.2 中文破解版(附使用教程) 64位

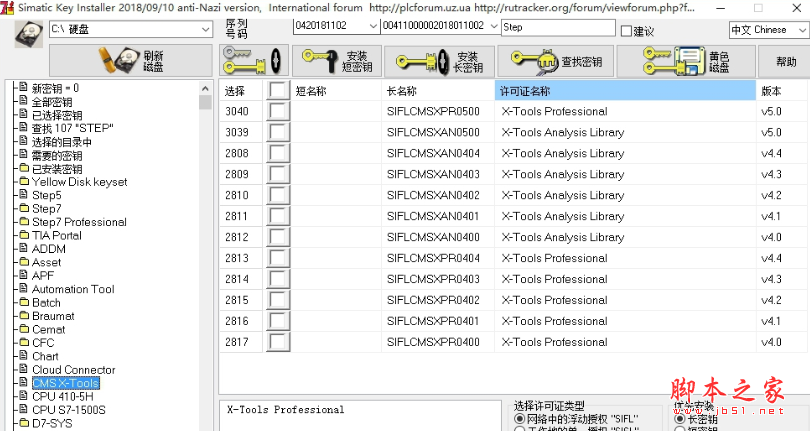

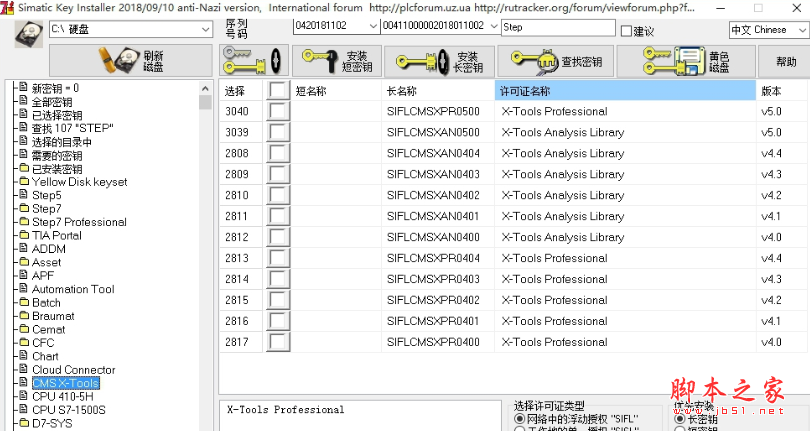

西门子全系列软件授权工具Sim EKB Install v2023.11.24 最新绿色

ANSYS Products 2024 R2.03 (SP3) x64 中文免费授权版(附安装教

Sidefx Houdini FX(电影特效魔术师) v12.5 2013 english 附详细

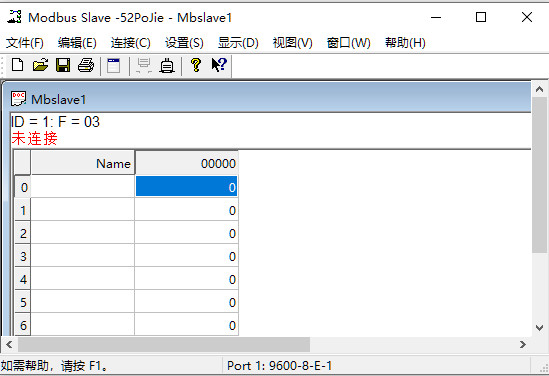

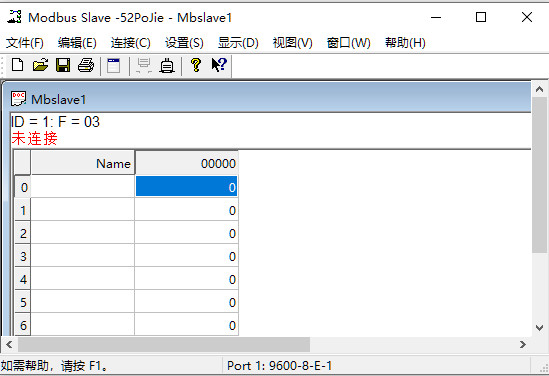

Modbus slave调试工具 v7.4.4 绿色免安装汉化版 64位

KISSsoft 2022 SP3-SP5 x64 中文免费破解版(附许可文件+教程)

西门子PCL编程软件STEP7 MicroWIN SMART V2.8 官方最新版

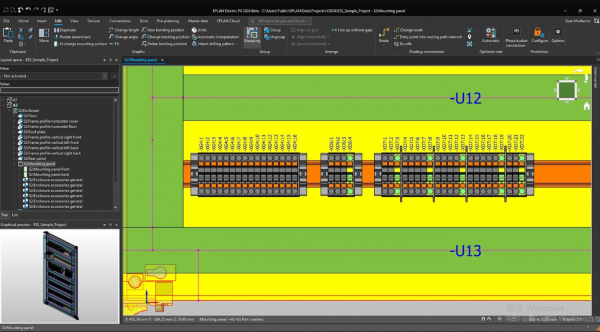

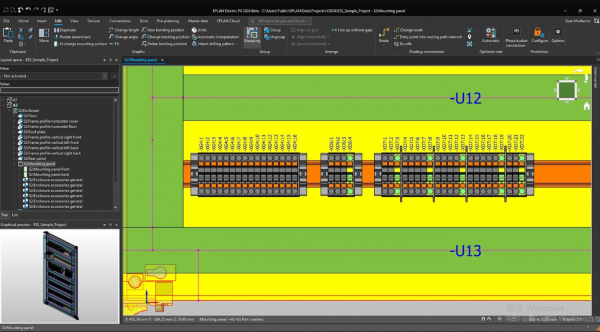

EPLAN Electric P8 2024.0.3 (21408) x64 中文完美激活版(附安装

EPLAN Electric P8 2022 中文授权破解版(含补丁+安装教程)

相关文章

-

Siemens SIMATIC PCS 7 V10 2023.7 中文完整授权版(附教程)

Siemens SIMATIC PCS 7 V10 2023.7 中文完整授权版(附教程)SIMATIC PCS 7是一款性能可靠的分布式控制系统,先进的过程控制系统非常适合工厂应用,作为强大的系统,它具有灵活的适应性,该系统可确保工厂全生命周期中的平稳流程、优...

-

CNC编程软件 GibbsCAM 2025 v25.0.41.0 x64 中文授权免费版(附安装教程)

CNC编程软件 GibbsCAM 2025 v25.0.41.0 x64 中文授权免费版(附安装教程)GibbsCAM是一款易于学习且直观的CAM软件,非常适合企业中的各类用户。无论您是经验丰富的技术专家还是刚入门的新手,GibbsCAM的高效编程能力都能帮助您实现最高75%的编程效...

-

Cadence SPB OrCAD X/Allegro X Design Platform 2024 v24.10.000 完整免费版

Cadence SPB OrCAD X/Allegro X Design Platform 2024 v24.10.000 完整免费版Cadence设计系统公司发布了Cadence OrCAD X Design Platform 2024 (OrCAD X and Allegro X),此次更新的重点是可用性、集成分析和自动化,包括BOM预测和预测分析、数据管理...

-

齿轮设计软件 KISSsoft 2024 SP2 x64 中文免费版(附安装教程)

齿轮设计软件 KISSsoft 2024 SP2 x64 中文免费版(附安装教程)KISSsoft 2024是一款专业的齿轮传动设计分析软件,它是用于设计、优化和分析机器元件的模块化计算系统,广泛应用于工业领域、航空航天领域、车辆行业等,本次提供的是KISSs...

-

Keysight PathWave Advanced Design System (ADS) 2025 完整版(附安装教程)

Keysight PathWave Advanced Design System (ADS) 2025 完整版(附安装教程)Advanced Design System (ADS) 2025又称高级软件设计系统,是由Keysight是德科技公司开发的电子设计自动化软件,适用于射频、微波和信号完整性应用,本次提供的是ADS2025最...

-

EPLAN Electric P8 2025 v2025.0.0.0 官方正式安装版

EPLAN Electric P8 2025 v2025.0.0.0 官方正式安装版EPLAN Electric P8 2025正式版目前已经发布了,是一款功能强大的电气工程设计软件,新版本对PLC、电缆、端子进行了更新,创新的功能和改善将使您的设计更加高效...

下载声明

☉ 解压密码:www.jb51.net 就是本站主域名,希望大家看清楚,[ 分享码的获取方法 ]可以参考这篇文章

☉ 推荐使用 [ 迅雷 ] 下载,使用 [ WinRAR v5 ] 以上版本解压本站软件。

☉ 如果这个软件总是不能下载的请在评论中留言,我们会尽快修复,谢谢!

☉ 下载本站资源,如果服务器暂不能下载请过一段时间重试!或者多试试几个下载地址

☉ 如果遇到什么问题,请评论留言,我们定会解决问题,谢谢大家支持!

☉ 本站提供的一些商业软件是供学习研究之用,如用于商业用途,请购买正版。

☉ 本站提供的Mentor Graphics HDL Designer Series(HDS) v2021.1.1 许可激活版(附补丁)资源来源互联网,版权归该下载资源的合法拥有者所有。